LDO模拟集成电路设计 从原理到实践

LDO(Low Dropout Regulator,低压差线性稳压器)是模拟集成电路设计中一类至关重要的电源管理器件,广泛应用于各类电子系统中,为敏感电路提供稳定、低噪声的供电电压。其设计融合了模拟集成电路设计的核心思想与针对特定功能的优化策略。

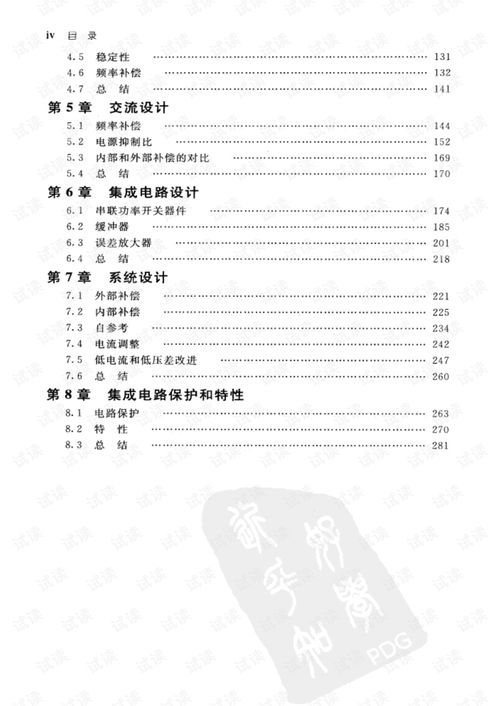

1. LDO的基本工作原理与核心指标

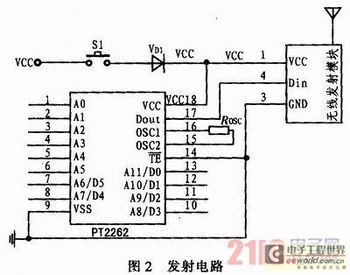

LDO本质上是一个负反馈系统。其基本结构通常包含误差放大器(EA)、功率调整管(Pass Transistor,通常为PMOS或PNP型)、反馈电阻网络以及负载。误差放大器持续比较反馈电压(由输出电压分压得到)与基准电压(Bandgap Reference)的差值,并通过驱动功率调整管来调整其导通状态,从而稳定输出电压。

LDO的关键性能指标包括:

- 压差电压(Dropout Voltage):维持规定稳压精度时,输入与输出电压之间的最小差值。低压差是现代LDO的核心优势,尤其适用于电池供电场景。

- 静态电流(Quiescent Current, IQ):LDO自身工作所消耗的电流,直接影响系统待机时间。低IQ设计是便携设备的关键。

- 负载调整率(Load Regulation):负载电流变化时输出电压的稳定能力。

- 线性调整率(Line Regulation):输入电压变化时输出电压的稳定能力。

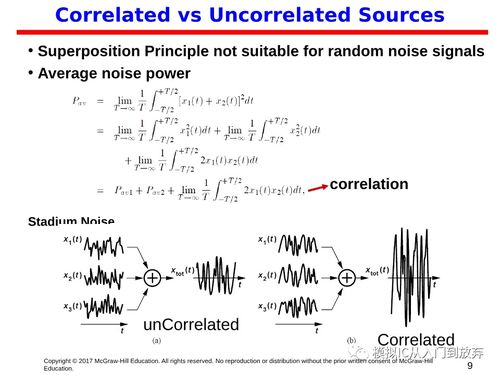

- 电源抑制比(PSRR):衡量LDO抑制输入电源纹波和噪声的能力,对于射频、音频等敏感电路至关重要。

- 瞬态响应(Transient Response):负载电流发生阶跃变化时,输出电压的过冲/下冲及恢复时间。

2. LDO设计的核心挑战与电路技术

LDO设计并非简单的误差放大与调整,它面临一系列相互制约的挑战:

稳定性与补偿:LDO是一个条件稳定系统。其环路稳定性受输出电容(包括ESR)、负载电流大小等因素的显著影响。为确保在全负载范围和温度下稳定,必须采用精密的补偿技术。常见的补偿方法包括:

- 主极点补偿:在误差放大器输出端(即功率管栅极)形成主极点。

- 米勒补偿:利用功率管本身的米勒电容进行补偿,能有效节省面积。

- 前馈补偿:在反馈网络中引入零点,以抵消输出极点的影响,改善瞬态响应。

功率管设计:作为电流通路的核心,功率管的选择(PMOS vs. PNP)和尺寸设计直接影响压差、驱动能力、瞬态响应和芯片面积。PMOS功率管因其易于集成和低驱动电流需求而更常见于CMOS工艺中。

基准源与误差放大器:一个高精度、低温度漂移的带隙基准电压源是LDO性能的基础。误差放大器则需要高增益、高PSRR和足够的摆幅,其架构(如折叠式共源共栅、两级运放等)需根据整体性能折中选择。

瞬态响应优化:快速的瞬态响应需要环路具有高带宽,但这与稳定性要求相冲突。设计师常采用额外的瞬态增强电路,如采用辅助的快速通路(Slew-Rate Enhancement Circuit)或动态偏置技术,在负载跳变时瞬间提供或吸收大电流,以最小化输出电压波动。

无电容LDO(Capacitor-Less LDO):为节省外部元件成本和PCB面积,无电容LDO成为研究热点。它通过创新的内部补偿和频率响应整形技术,在不依赖外部大电容ESR的情况下实现稳定,但通常对设计复杂度和工艺变化更敏感。

3. LDO在整体集成电路设计流程中的位置

LDO设计是典型的模拟/混合信号IP设计流程:

- 指标定义:根据系统需求(如输入/输出电压范围、最大负载电流、静态功耗预算、PSRR要求等)确定设计规格。

- 架构选择:基于工艺和指标,确定整体架构(如是否采用无电容结构、补偿方案、功率管类型)。

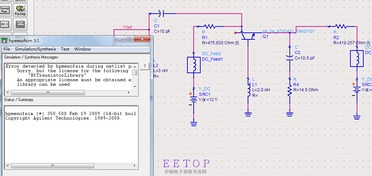

- 电路设计与仿真:使用EDA工具(如Cadence Virtuoso)进行晶体管级设计,并通过仿真(DC、AC、瞬态、蒙特卡洛、PVT角仿真)验证各项指标。

- 版图设计:考虑匹配、噪声、电流密度、ESD、latch-up等因素进行物理实现。功率管的布局、走线宽度(承受大电流)和散热设计尤为关键。

- 后仿真与验证:提取版图寄生参数后,再次进行全面的仿真验证,确保性能达标。

- 流片与测试:交付给晶圆厂制造,随后进行硅片测试,验证实际性能。

4. 发展趋势

随着工艺节点不断进步和系统级封装(SiP)的普及,LDO设计正朝着以下方向发展:

- 超低功耗与高能效:适应物联网设备的需求,静态电流已可低至数十纳安。

- 高集成度:作为电源管理单元(PMU)的一部分,与DCDC转换器、充电管理等模块集成。

- 数字化辅助与自适应:引入简单的数字电路(如轻负载检测、环路参数自适应调整)以优化不同工作状态下的性能。

- 先进工艺下的挑战:在纳米级CMOS工艺下,电源电压降低,晶体管阈值电压未同比缩放,给设计高精度、低压差LDO带来新挑战。

###

LDO模拟集成电路设计是理论与实践深度结合的典范。它要求设计师深刻理解反馈控制理论、半导体器件物理、工艺特性以及系统应用需求,并在性能、面积、功耗和成本之间做出精妙的权衡。一个优秀的LDO设计,不仅仅是电路原理图的实现,更是对稳定性、鲁棒性和实用性的全方位考量,是模拟集成电路设计智慧的集中体现。

如若转载,请注明出处:http://www.xjioter.com/product/13.html

更新时间:2026-03-13 05:38:00