集成电路设计中的关键环节 版图设计

集成电路设计是一个复杂而精密的系统工程,它从抽象的概念和算法出发,最终转化为物理上可制造的硅芯片。在这一系列流程中,版图设计扮演着至关重要的角色,是连接逻辑设计与物理实现的桥梁。

一、版图设计的核心定位

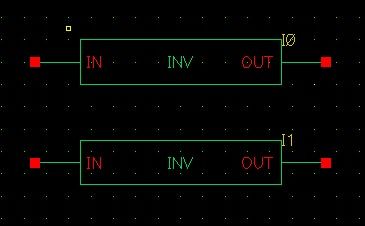

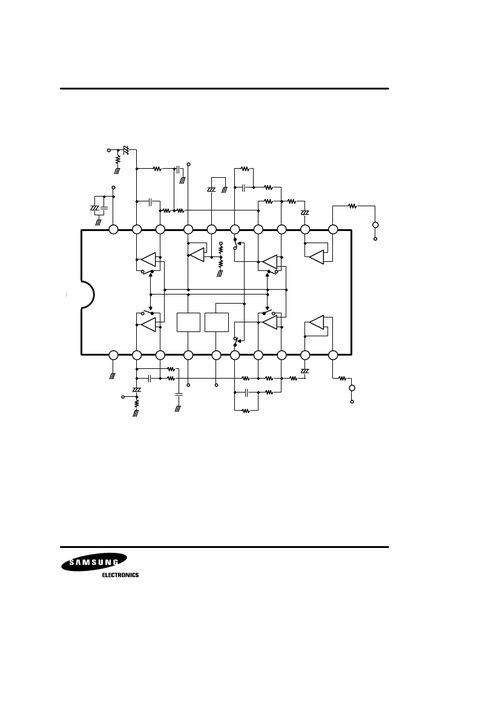

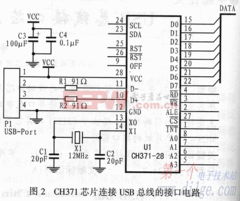

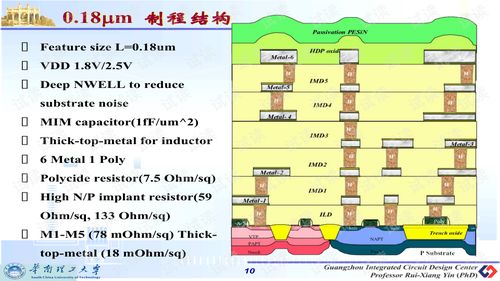

版图设计,又称为物理设计,是在电路逻辑设计完成之后的关键步骤。设计师需要将用硬件描述语言(如Verilog、VHDL)定义好的电路网表,根据特定的半导体工艺规则,转换成一系列几何图形。这些图形定义了构成芯片的每一层——如扩散层、多晶硅层、金属互连层——的形状、尺寸和位置。换言之,版图就是芯片的“施工蓝图”,直接决定了芯片的性能、功耗、面积和可靠性。

二、版图设计的主要流程与挑战

一个典型的版图设计流程通常包含以下几个核心阶段:

- 布局规划:确定芯片上各个功能模块(如存储器、运算单元)的宏观位置和整体芯片的形状。目标是优化信号流、降低互连延迟并控制芯片面积。

- 布图:将标准单元和宏模块精确地放置到芯片的规划区域内。

- 时钟树综合:构建一个均衡的时钟分布网络,确保时钟信号能够同时、低偏差地到达所有时序单元,这是保证芯片高速稳定运行的关键。

- 布线:根据电路的电气连接关系,在多层金属中为所有信号和电源/地线规划并绘制出物理连线。这需要解决复杂的路径寻找、串扰规避和通孔优化问题。

- 物理验证:这是确保设计可制造、功能正确的最后关卡。主要包括:

- 设计规则检查:确保版图完全符合晶圆代工厂的工艺制造极限(如最小线宽、间距)。

- 电路图与版图一致性检查:确保物理版图与原始电路逻辑网表在电气连接上完全匹配。

- 电气规则检查:检查天线效应、静电放电保护等电气可靠性问题。

整个过程中,设计师必须在性能(速度)、功耗、面积(成本)和设计周期之间进行精妙的权衡与优化。

三、先进工艺下的版图设计新趋势

随着工艺节点不断演进至7纳米、5纳米乃至更先进水平,版图设计面临着前所未有的挑战:

- 物理效应加剧:短沟道效应、线电阻/电容增大、电源电压降低等,使得时序收敛和功耗控制变得极其困难。

- 设计规则复杂化:多重曝光、自对准多重图案等新技术带来了极其复杂和限制性的设计规则。

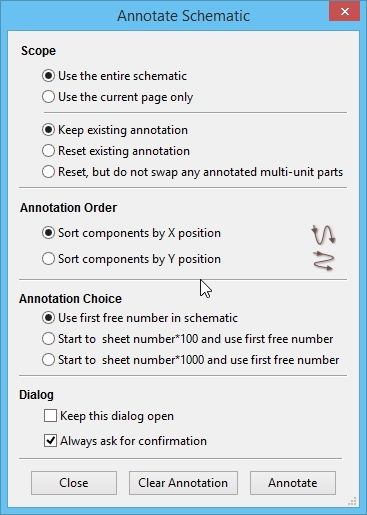

- 对EDA工具的深度依赖:完全依赖手工设计已不现实,自动化布局布线工具、签核分析工具的作用愈发核心。

因此,现代版图设计不仅是“绘图”工作,更需要设计师深刻理解器件物理、工艺制程和电路原理,并与EDA工具进行高效互动,采用如模块化设计、层次化设计等策略来管理复杂度。

###

集成电路版图设计是想象力与精密工程的交汇点。它将无形的电子思想,塑造成有形的、功能强大的硅基实体。在摩尔定律持续推进的今天,优秀的版图设计是释放先进工艺潜力、实现高性能、低功耗芯片不可或缺的基石。掌握其原理与艺术,是每一位集成电路设计工程师通向卓越的必经之路。

如若转载,请注明出处:http://www.xjioter.com/product/1.html

更新时间:2026-03-13 23:32:03